When the third clock pulse arrives this logic “1” value moves to the output of FFC ( Q C ) and so on until the arrival of the fifth clock pulse which sets all the outputs Q A to Q D back again to logic level “0” because the input to FFA has remained constant at logic level “0”. The logic “1” has now moved or been “shifted” one place along the register to the right as it is now at Q A. The second clock pulse will change the output of FFA to logic “0” and the output of FFB and Q B HIGH to logic “1” as its input D has the logic “1” level on it from Q A. Assume now that the DATA input pin of FFA has returned LOW again to logic “0” giving us one data pulse or 0-1-0. If a logic “1” is connected to the DATA input pin of FFA then on the first clock pulse the output of FFA and therefore the resulting Q A will be set HIGH to logic “1” with all the other outputs still remaining LOW at logic “0”. Lets assume that all the flip-flops ( FFA to FFD ) have just been RESET ( CLEAR input ) and that all the outputs Q A to Q D are at logic level “0” ie, no parallel data output.

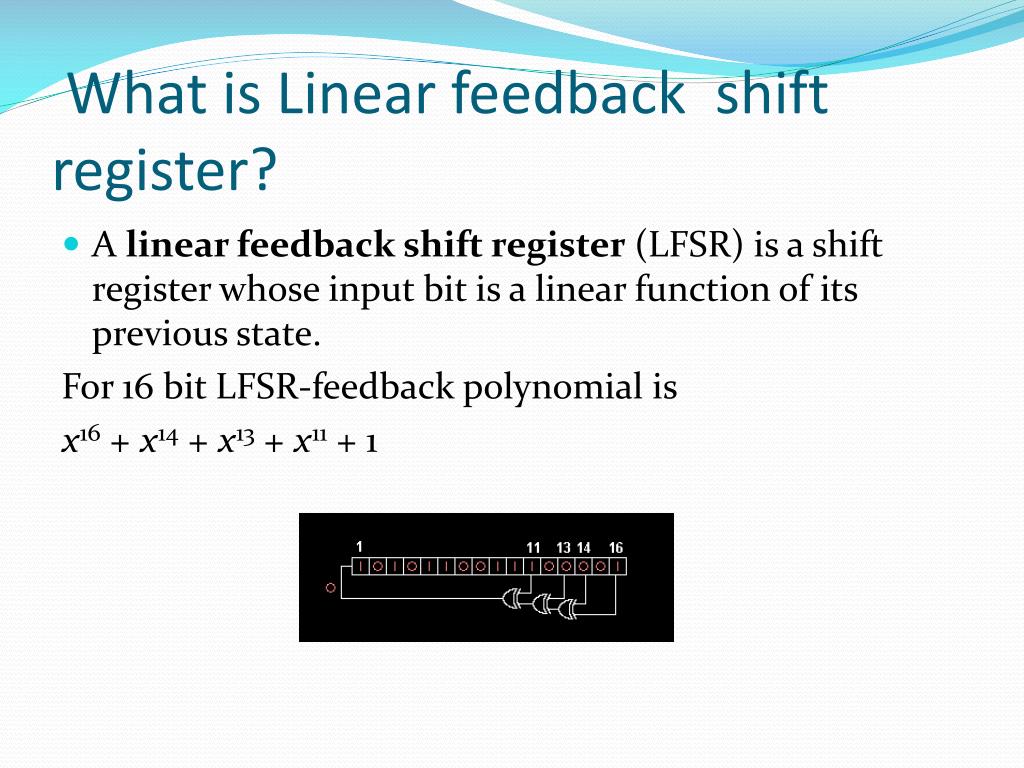

The effect of data movement from left to right through a shift register can be presented graphically as: Parallel-in to Parallel-out (PIPO) – the parallel data is loaded simultaneously into the register, and transferred together to their respective outputs by the same clock pulse.Parallel-in to Serial-out (PISO) – the parallel data is loaded into the register simultaneously and is shifted out of the register serially one bit at a time under clock control.Serial-in to Serial-out (SISO) – the data is shifted serially “IN” and “OUT” of the register, one bit at a time in either a left or right direction under clock control.

Serial-in to Parallel-out (SIPO) – the register is loaded with serial data, one bit at a time, with the stored data being available at the output in parallel form.Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: Shift register IC’s are generally provided with a clear or reset connection so that they can be “SET” or “RESET” as required. The individual data latches that make up a single shift register are all driven by a common clock ( Clk ) signal making them synchronous devices. Shift Registers are used for data storage or for the movement of data and are therefore commonly used inside calculators or computers to store data such as two binary numbers before they are added together, or to convert the data from either a serial to parallel or parallel to serial format.

0 kommentar(er)

0 kommentar(er)